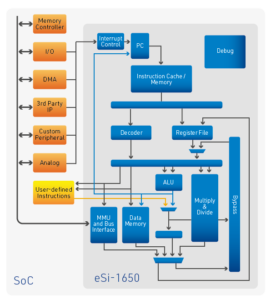

eSi-1650

16位精简指令架构(RISC)处理器 – 带缓存的低成本 & 低功耗CPU

eSi-1650 是一款核心面积很小,功耗很低,但是带有指令缓存的16位CPU。 由于其具有较小的逻辑门数量同时又带有指令缓存,所以在使用OTP或Flash作为程序内存的制程下,eSi-1650可以提供非常好的能效比。

文档下载

下载…

eSi-RISC手册

eSi-1650手册

eSi-RISC架构手册(需要签订NDA)

16位精简指令(RISC)IP:eSi-1650技术总览

技术特性

- 16位精简指令(RISC)结构

- 16或者32个通用寄存器

- 92条基本指令,10种寻址模式

- 最多支持74条用户自定义指令

- 5级流水线

- 可选内存保护单元(MPU)

- 可配置的指令缓存(1-64kB,直接映射或2路4路相连映射)

- AMBA AHB总线,APB外设总线

- 灵活可选的用户态和特权态支持

- 最大支持16个中断向量,支持不可屏蔽中断(NMI)和系统调用

- 支持硬件嵌套和优先级抢断中断

- 快速中断响应,只需要6~9个时钟周期

- 支持JTAG或串口调试,可选硬件性能计数(PMU)及跟踪支持

- 最大2.81 CoreMark/MHzUp

- 支持多核

- 支持混合使用16位和32位指令,在略微牺牲性能的情况下极大的提高代码密度

- ASIC性能数据(典型的情况是在28纳米制程下):

- 主频可达1GHz

- 最小只耗用10000个逻辑门

- 能耗比低至3uW/MHz

- 高质量的IP:

- 采用Verilog RTL设计

- 设计时充分考虑DFT

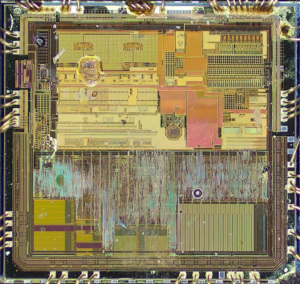

- 经过工业界量产检验

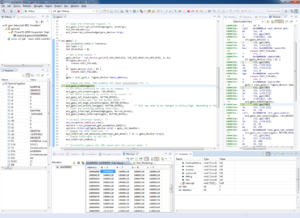

- C/C++软件开发环境基于免授权费的工具链。开发环境采用业界主流的Eclipse集成开发环境

- 迁移到不带缓存的16位版本或者32位版本非常容易

核心架构

eSi-1650是一款带有指令缓存的16位CPU。它主要面向目前采用8位CPU的低功耗的应用场景,或者那些32位处理器在面积或功耗太大的场景。 通过集成指令缓存,在使用片上NVM核Flash作为程序内存的情况下,eSi-1650可以提供较高的性能,同时核心面积核功耗控制在较低的水平。

由于CPU主频主要受限于内存的速率,通过使用缓存,在成熟的制程下eSi-1650可以达到更高的主频。 使用缓存同时带来整体功耗的降低,因为读缓存比读Flash功耗低。 指令缓存可以小于一块完整的影子RAM(shadow RAM)。

由于采用了精简指令(RISC)流水线,虽然eSi-1650是16位处理器,它的逻辑门数量却跟8位处理器一样少。 在数据通路和寄存器都是16位的情况下,运行应用程序需要的时钟周期更少。 因此,可以通过CPU降频或者让CPU更快的进入省电模式来节省大量的能耗。

eSi-1650的指令集支持丰富的算数运算,比如32位整数乘除,累乘。 它同时提供一系列的应用场景可选指令和寻址模式。 支持位操作指令,比如位提取,位插入,clz,popcnt,ffs和位翻转等。 支持整数平方根,绝对值,min/max,crc和partiy指令。 Wait-for-interrupt指令允许快速的进入低功耗状态,支持对时钟频率和功耗进行限制。

对于那些需要极高的性能或者极低的功耗的场景,可以通过用户自定义指令和寄存器来支持实现。

同时支持用户态和核心态,特权指令和内存保护可以通过可选的MPU实现,操作系统可以跟应用程序有效隔离,从而得到充分的保护。

硬件调试支持硬件断点,观察点,跟踪,性能计数器,空指针探测,单步。这些特性可以有效的支撑对运行在ROM,FLASH和RAM上的程序进行快速调试。

工具链

工具链基于业界标准的GNU工具链,包含C/C++优化编译器,汇编器,链接器,调试器,仿真器和其他二进制工具。 所有的这些工具同时支持集成到Eclipse IDE中,或者作为命令行工具直接调用。

调试器可以通过低成本的USB-JTAG转换器连接到硬件调试对象,也可以通过Verilog PLI库运行RTL仿真。

支持完整的C/C++库。 带eSi-RISC支持的Micrium uC/OS-II RTOS,ThreadX,FreeRTOS。这些RTOS还支持lwIP TCP/IP协议栈。 工具链支持Windows,Linux两种平台。工具链不收取额外的授权费。

IP发布

eSi-1650以Verilog RTL IP核的形式发布。 我们的设计非常的中性,不偏向特别的技术框架。 设计时充分考虑了测试,考虑了DFT,支持在所有的时钟沿插入扫描,还支持内存BIST。 对于常用的EDA工具,我们提供一系列的脚本范例。

跟随处理器核,我们同时提供一系列基于AMBA总线的周边,包括:UART,SPI,I2C™,I2S,Timer,PWM,Watchdog,GPIO,PS/2,RTC,Ethernet MAC,USB,FIFO,Scatter-Gather DMA,AES,SHA,ECC和quad-SPI闪存接口。 得益于使用业界标准的总线协议,eSi-1650同时兼容广泛的第三方IP。

根据客户的需求,我们可以生成多层的AHB矩阵和APB总线来连接eSi-1650处理器,内存和外设。