eSi-TSMC Flash

## **1** Contents

| 1   | Contents                  | 2  |

|-----|---------------------------|----|

| 2   | Overview                  | 3  |

| 3   | Hardware Interface        | 4  |

| 4   | Software Interface        | 7  |

| 4.1 | Register Map              | 7  |

| 4.2 | Register Write Protection | 11 |

| 4.3 | Flash Operations          | 12 |

| 5   | Revision History          | 14 |

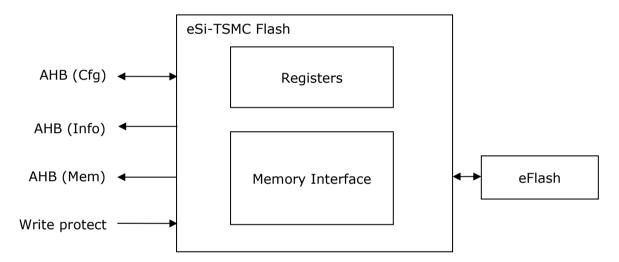

## 2 Overview

The eSi-TSMC Flash core provides an interface a TSMC embedded flash. It supports the following features:

- Supports access to one data memory and one information memory.

- Optionally supports redundancy.

- Optional ECC support with SECDEC (single-bit error correction, double-bit error detection).

- Programmable read/write timings, to support different clock frequencies.

- Write protection.

- Discharge on brown out.

- Triple AMBA 3 AHB-lite slave interfaces:

- $\circ$   $\$  cfg for configuration and programming.

- mem for memory read accesses.

- o info for information page read accesses.

#### Figure 1: eSi-TSMC Flash

# **3** Hardware Interface

| Module Name  | cpu_ahb_tsmc_flash   |

|--------------|----------------------|

| HDL          | Verilog              |

| Technology   | Generic              |

| Source Files | cpu_ahb_tsmc_flash.v |

| Port                     | Туре    | Description                                                 |

|--------------------------|---------|-------------------------------------------------------------|

| xadr_pins                | Integer | Width of X address bus to flash                             |

| yadr_pins                | Integer | Width of Y address bus to flash                             |

| data_pins                | Integer | Number of pins in data bus used for data                    |

| address_pins             | Integer | Width of internal address bus wide enough to access         |

|                          |         | all addresses in flash data block:                          |

|                          |         | <pre>(xadr_pins+yadr_pins+log2(data_pins/8))</pre>          |

| ecc_pins                 | Integer | Number of bit in data bus used for ECC                      |

| recall_on_first_read     | Integer | Determines whether a recall operation will                  |

|                          |         | automatically be performed on the first memory read         |

| bias_initial             | Integer | Determines whether the "bias initial" test mode             |

|                          |         | sequence is performed before erase reference cell           |

| info_pages               | Integer | How many information pages are implemented                  |

| read_wait_states         | 5:0     | Reset value for timing0.R                                   |

| five_us_reset            | 15:0    | Reset value for timing0.F                                   |

| erase_cycles_reset       | 23:0    | Reset value for timing1.E                                   |

| program_cycles_reset     | 15:0    | Reset value for timing2.P                                   |

| hundred_ns_reset         | 7:0     | Reset value for timing2.H                                   |

| ten_ns_reset             | 3:0     | Reset value for timing2.T                                   |

| resume_after_brownout    | Boolean | Whether flash operation can continue after brown out        |

| write_protect_privileged | Boolean | Whether control.WP must be clear to allow privileged writes |

### **Table 1: Parameters**

| Port               | Direction | Width      | Description                                                                                                                                 |

|--------------------|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| write_protect_all  | Input     | 1          | Prevents all write and erase operations                                                                                                     |

| write_protect      | Input     | 32         | Data bock write protection flags                                                                                                            |

| info_write_protect | Input     | info_pages | Information block write protection flags                                                                                                    |

| disable_redundancy | Input     | 1          | Disables use of redundancy information                                                                                                      |

| brown_out          | Input     | 1          | Power brown out indicated. When<br>asserted, the controller will perform the<br>discharge sequence if occurs during erase<br>or programming |

| discharged         | Output    | 1          | Indicates discharge sequence is complete after brown out                                                                                    |

| mem_hclk           | Input     | 1          | Memory interface, AHB clock                                                                                                                 |

| mem_hresetn        | Input     | 1          | Memory interface, AHB reset, active-low                                                                                                     |

| mem_haddr          | Input     | BITS       | Memory interface, AHB address                                                                                                               |

| mem_hburst         | Input     | 3          | Memory interface, AHB burst type                                                                                                            |

| mem_hmastlock      | Input     | 1          | Memory interface, AHB locked transfer                                                                                                       |

| mem_hprot          | Input     | 4          | Memory interface, AHB protection                                                                                                            |

| mem_hsize          | Input     | 3          | Memory interface, AHB size                                                                                                                  |

| mem_htrans         | Input     | 2          | Memory interface, AHB transfer type                                                                                                         |

| mem_hwdata         | Input     | BITS       | Memory interface, AHB write data                                                                                                            |

| mem_hwrite         | Input     | 1          | Memory interface, AHB write                                                                                                                 |

| mem_hready         | Input     | 1          | Memory interface, AHB ready                                                                                                                 |

# eSI-RISC

| men_bready         Input         1         Memory interface, AHB select           men_bready         Output         1         Memory interface, AHB ready           info_holk         Input         1         Memory interface, AHB ready           info_holk         Input         1         Info page interface, AHB response           info_holk         Input         1         Info page interface, AHB decks           info_holks         Input         3         Info page interface, AHB decks           info_holks         Input         3         Info page interface, AHB decks           info_holks         Input         3         Info page interface, AHB solved           info_holks         Input         3         Info page interface, AHB wite           info_holks         Input         1         Info page interface, AHB wite           info_hokita         Input         1         Info page interface, AHB wite           info_hokita         Input         1         Info page interface, AHB wite           info_heredy         Output         1         Info page interface, AHB wite           info_heredy         Output         1         Info page interface, AHB wite           info_heredy         Output         1         Info page interface, AHB wite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5               |         |          |                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|----------|-----------------------------------------|

| mem_hrespOutputBITSMemory interface, AHB read datamem_hrespOutput1Memory interface, AHB read, active-lowinfo_hclkInput1Info page interface, AHB clockinfo_hclkInputBITSInfo page interface, AHB badressinfo_hburstInput3Info page interface, AHB locked transferinfo_hburstInput3Info page interface, AHB read, active-lowinfo_hburstInput3Info page interface, AHB read, active-lowinfo_hbarstInput4Info page interface, AHB read, active-lowinfo_htransInput2Info page interface, AHB read, active-lowinfo_htransInput1Info page interface, AHB read, active-lowinfo_headaInput1Info page interface, AHB read, active-lowinfo_headaInput1Info page interface, AHB read, active-lowinfo_headInput1Info page interface, AHB read, active-lowinfo_hreadyUnput1Info page interface, AHB read, active-lowinfo_hreadaOutput1Info page interface, AHB read, active-lowinfo_hreadaOutput1Info page interface, AHB read, active-lowinfo_hreadaInput1Info page interface, AHB read, active-lowinfo_hreadaOutput1Info page interface, AHB read, active-lowinfo_hreadaInput1Info page interface, AHB read, active-lowinfo_hreadaInput1Info page interface, AHB read, active-lowinfo_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | mem_hsel        | Input   | 1        | Memory interface, AHB select            |

| mem         Interact         Output         BITS         Memory interface, AHB read data           mem         Info         Info         Nemory interface, AHB read data           info         Info         Info         page interface, AHB response           info         Info         Info         page interface, AHB response           info         Info         Info         page interface, AHB address           info         Info         Info         page interface, AHB         active-low           info         Info         Info         page interface, AHB         active-low           info         Input         Info         Info         page interface, AHB         active-low           info         Input         Info         page interface, AHB         active-low           info         Input         Info         page i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mem_hready      | Output  | 1        | Memory interface, AHB ready             |

| mem_brespOutput1Memory interface, AHB responseinfo_hresetnInput1Info page interface, AHB clockinfo_haddrInput1Info page interface, AHB clockinfo_haddrInput1Info page interface, AHB burst typeinfo_haddrInput3Info page interface, AHB burst typeinfo_haddrInput3Info page interface, AHB brotectioninfo_hadarInput4Info page interface, AHB protectioninfo_hatarInput3Info page interface, AHB readyinfo_hatarInput1Info page interface, AHB readyinfo_hatarInput1Info page interface, AHB readyinfo_hatarInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyInput1Configuration interface, AHB readyinfo_hreadyInput1Configuration interface, AHB readyinfo_hreadyInput3Configuration interface, AHB readycfg_hreadyInput3Configuration interface,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mem_hrdata      | Output  | BITS     | Memory interface, AHB read data         |

| info_helkInput1Info page interface, AHB clockinfo_haddrInputBITSInfo page interface, AHB clockinfo_haddrInputBITSInfo page interface, AHB clocked transferinfo_hadlockInput1Info page interface, AHB locked transferinfo_hadlockInput3Info page interface, AHB sizeinfo_hadlockInput3Info page interface, AHB sizeinfo_hatzeInput3Info page interface, AHB sizeinfo_hataaInput1Info page interface, AHB writeinfo_hataaInput1Info page interface, AHB writeinfo_hataaInput1Info page interface, AHB writeinfo_hataaInput1Info page interface, AHB selectinfo_hreadyOutput1Info page interface, AHB selectinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyInput1Configuration interface, AHB dockscfg_hreadInput1Configuration interface, AHB dockscfg_hreadInput2Configuration interfac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mem_hresp       | Output  | 1        |                                         |

| info_hresstnInput1Info page interface, AHB reset, active-lowinfo_hburstInputBITSInfo page interface, AHB burst typeinfo_hburstInput3Info page interface, AHB burst typeinfo_hprotInput1Info page interface, AHB burst typeinfo_hastlockInput3Info page interface, AHB protectioninfo_hatzeInput3Info page interface, AHB write datainfo_hataInput1Info page interface, AHB readyinfo_hataInput1Info page interface, AHB readyinfo_hreadyInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyifg_hreadxInput3Configuration interface, AHB readyifg_hreadxInput3Conf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | info hclk       | Input   | 1        |                                         |

| into_haddrInputBITSInfo page interface, AHB burst typeinto_hmastlockInput1Info page interface, AHB burst typeinto_hmastlockInput1Info page interface, AHB blocked transferinfo_hsizeInput3Info page interface, AHB sizeinfo_htransInput3Info page interface, AHB sizeinfo_htransInput2Info page interface, AHB write datainfo_htransInput1Info page interface, AHB writeinfo_htransInput1Info page interface, AHB writeinfo_htransInput1Info page interface, AHB writeinfo_htradyInput1Info page interface, AHB selectinfo_htradaOutput1Info page interface, AHB readyinfo_htradaOutput1Info page interface, AHB case, active-lowcfg_htrastInput1Configuration interface, AHB case, active-lowcfg_htrastInput3Configuration interface, AHB lockedtrastInput3Configuration interface, AHB sizecfg_htrastInput3Configuration interface, AHB sizecfg_htrastInput3Configuration interface, AHB sizecfg_htrastInput3Configuration interface, AHB sizecfg_htrastInput4Configuration interface, AHB sizecfg_htrastInput3Configuration interface, AHB sizecfg_htrastInput3Configuration interface, AHB sizecfg_htrastInput </td <td>info hresetn</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | info hresetn    |         |          |                                         |

| intoIntoJuntJuntJuntJuntintoInput1Info page interface, AHB burst typeintoIntoInput1Info page interface, AHB protectionintoInfoInfoJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoInfoJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJuntJuntinfoJuntJuntJunt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _               |         |          |                                         |

| info_hprotInput1Info page interface, AHB locked transferinfo_hprotInput4Info page interface, AHB sizeinfo_hsizeInput3Info page interface, AHB sizeinfo_htransInput2Info page interface, AHB write datainfo_htransInput1Info page interface, AHB write datainfo_htransInput1Info page interface, AHB write datainfo_htradyInput1Info page interface, AHB readyinfo_htradyOutput1Info page interface, AHB readyinfo_htradyOutput1Configuration interface, AHB case, active-lowcfg_htradInput3Configuration interface, AHB datesscfg_htradInput3Configuration interface, AHB brast typecfg_htradInput3Configuration interface, AHB transfer typecfg_htradInput3Configuration interface, AHB transfer typecfg_htradInput3Configuration interface, AHB transfer typecfg_htradInput3Configuration interface, AHB transfer typecfg_htradInput1Configuration interface, AHB transfer typecfg_htradInput1Configuration interface, AHB transfer type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _               |         | 3        |                                         |

| info_hprotInput4Info page interface, AHB protectioninfo_hsizeInput3Info page interface, AHB transfer typeinfo_hvataaInput2Info page interface, AHB transfer typeinfo_hvataaInput1Info page interface, AHB writeinfo_hreadyInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB reset, active-info_hreadyOutput1Info page interface, AHB reset, active-info_hreadyInput1Configuration interface, AHB burst typecfg_haddrInput3Configuration interface, AHB burst typecfg_hburstInput3Configuration interface, AHB sizecfg_hbrastInput3Configuration interface, AHB sizecfg_htransInput3Configuration interface, AHB sizecfg_htransInput1Configuration interface, AHB sizecfg_htransInput2Configuration interface, AHB sizecfg_htransInput1Configuration interface, AHB sizecfg_htransInput1Configuration interface, AHB sizecfg_htransInput1Configuration interface, AHB sizecfg_htransInput1Configuration interface, AHB readycfg_htransIn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _               |         |          |                                         |

| Info_nsizeInput3Info page interface, AHB sizeinfo_htransInput2Info page interface, AHB write transfer typeinfo_hwriteInputInfo page interface, AHB write datainfo_hreadyInput1Info page interface, AHB writeinfo_hreadyInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadaOutput1Configuration interface, AHB cockcfg_hclkInput1Configuration interface, AHB backcfg_hadarInput3Configuration interface, AHB burst typecfg_hadarInput3Configuration interface, AHB protectioncfg_haizeInput3Configuration interface, AHB protectioncfg_haizeInput3Configuration interface, AHB write datacfg_hransInput3Configuration interface, AHB readycfg_hransInput1Configuration interface, AHB write datacfg_hransInput1Configuration interface, AHB write datacfg_hransInput1Configuration interface, AHB write datacfg_hransInput1Configuration interface, AHB write datacfg_hransInput1Configuration interface, AHB write datacfg_hready <td< td=""><td>_</td><td></td><td>_</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _               |         | _        |                                         |

| into_transInput2Info page interface, AHB transfer typeinfo_hwdataInputBITSInfo page interface, AHB write datainfo_hreadyInput1Info page interface, AHB write datainfo_hreadyInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutputBITSInfo page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyInput1Configuration interface, AHB readyinfo_hreadyInput1Configuration interface, AHB readyinfo_hreadyInput1Configuration interface, AHB brackcfg_hattInput3Configuration interface, AHB brackedcfg_hattaInput3Configuration interface, AHB protectioncfg_hataInput2Configuration interface, AHB protectioncfg_hreadyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |         |          |                                         |

| info_hwataInputBITSInfo page interface, AHB write datainfo_hwriteInput1Info page interface, AHB readyinfo_hreadyInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB read datainfo_hreadyInput1Configuration interface, AHB readscfg_hclkInput1Configuration interface, AHB setex, active-cfg_hadarInput1Configuration interface, AHB backcfg_hhadrInput3Configuration interface, AHB burst typecfg_hnastlockInput3Configuration interface, AHB sizecfg_hransInput3Configuration interface, AHB sizecfg_hransInput3Configuration interface, AHB write datacfg_hransInput3Configuration interface, AHB writecfg_hransInput1Configuration interface, AHB readycfg_hransInput1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _               |         |          |                                         |

| info_hvriteInput1Info page interface, AHB writeinfo_hreadyInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutput1Configuration interface, AHB dockcfg_helkInput1Configuration interface, AHB burst typecfg_haddrInput1Configuration interface, AHB burst typecfg_hmastlockInput3Configuration interface, AHB sizecfg_hreadInput3Configuration interface, AHB sizecfg_hatasInput3Configuration interface, AHB readycfg_hatasInput3Configuration interface, AHB readycfg_hatasInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1 <t< td=""><td>_</td><td>-</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _               | -       |          |                                         |

| info_hreadyInput1Info page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB selectinfo_hreadyOutputBITSInfo page interface, AHB readyinfo_hreadyOutputInfo page interface, AHB readyinfo_hreadyOutput1Info page interface, AHB readycfg_hclkInput1Configuration interface, AHB reset, active-lowcfg_hresetnInput1Configuration interface, AHB burst typecfg_haddrInput3Configuration interface, AHB burst typecfg_hastlockInput1Configuration interface, AHB brotectioncfg_hastlockInput3Configuration interface, AHB protectioncfg_hransInput3Configuration interface, AHB protectioncfg_hransInput3Configuration interface, AHB write datacfg_hransInput1Configuration interface, AHB write datacfg_hwriteInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readydata_outOutputBITSConfiguration interface, AHB ready <t< td=""><td>_</td><td>-</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _               | -       |          |                                         |

| info_hselInput1Info page interface, AHB selectinfo_hreadyOutput1Info page interface, AHB readyinfo_hrespOutput1Info page interface, AHB read datainfo_hrespOutput1Info page interface, AHB read datainfo_hrespOutput1Configuration interface, AHB read datainfo_hrespInput1Configuration interface, AHB doresscfg_haddrInputBITSConfiguration interface, AHB burst typecfg_hmastlockInput3Configuration interface, AHB brotectioncfg_hsizeInput3Configuration interface, AHB protectioncfg_hsizeInput3Configuration interface, AHB protectioncfg_hataInput3Configuration interface, AHB protectioncfg_hataInput1Configuration interface, AHB protectioncfg_hataInput1Configuration interface, AHB readycfg_hataInput1Configuration interface, AHB readycfg_hataInput1Configuration interface, AHB readycfg_headyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —               |         |          |                                         |

| info_hreadyOutput1Info page interface, AHB readyinfo_hreadyOutputBITSInfo page interface, AHB readyatainfo_hreapOutput1Info page interface, AHB readyatainfo_hreapInput1Configuration interface, AHB reseponsecfg_hclkInput1Configuration interface, AHB reset, active-info_hreapInput1Configuration interface, AHB reset, active-info_hreapInputBITSConfiguration interface, AHB burst typecfg_haddrInput1Configuration interface, AHB burst typecfg_hastlockInput1Configuration interface, AHB reset, active-cfg_hsizeInput1Configuration interface, AHB burst typecfg_hransInput3Configuration interface, AHB reset, active-cfg_hransInput3Configuration interface, AHB reset, active-cfg_hransInput3Configuration interface, AHB reset, active-cfg_hransInput1Configuration interface, AHB readycfg_hradaInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB read datacfg_hreadyOutputBITSConfiguration interface, AHB read datacfg_hreapOutputBITSConfiguration interface, AHB read datacfg_hreapOutputBITSConfiguration interface, AHB read datacfg_hreapOutput <td< td=""><td>—</td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —               |         |          |                                         |

| info_hrdataOutputBITSInfo page interface, AHB read datainfo_hrespOutput1Info page interface, AHB responsecfg_holkInput1Configuration interface, AHB clockcfg_hresetnInput1Configuration interface, AHB ddresscfg_haddrInputBITSConfiguration interface, AHB burst typecfg_hmastlockInput3Configuration interface, AHB burst typecfg_hmastlockInput4Configuration interface, AHB protectioncfg_hsizeInput3Configuration interface, AHB transfercfg_htransInput2Configuration interface, AHB transfer typecfg_hwataInputBITSConfiguration interface, AHB write datacfg_heradyInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadOutput1Configuration interface, AHB readydata_inInput1Configuration interface, AHB readydata_inInput1Data outputdata_out_enableOutput1Data outputdata_out_enableOutput1Data outputyadrOutput1Sense anableyeeOutput1Sense anableyee <td< td=""><td>—</td><td>-</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —               | -       |          |                                         |

| info_hrespOutput1Info page interface, AHB responsecfg_hclkInput1Configuration interface, AHB clockcfg_hresetnInput1Configuration interface, AHB clockcfg_hburstInputBITSConfiguration interface, AHB addresscfg_hburstInput3Configuration interface, AHB burst typecfg_hastlockInput1Configuration interface, AHB burst typecfg_hastlockInput3Configuration interface, AHB sizecfg_hrastInput3Configuration interface, AHB sizecfg_htransInput2Configuration interface, AHB write datacfg_hwataInputBITSConfiguration interface, AHB write datacfg_hreadyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hrespOutput1Configuration interface, AHB readydata_outOutputecc_pins<br>+data_pinsData output enabledata_out_enableOutput1Flash data output enable, active-lowxadrOutput1Sense anableyadrOutput1Y addressyadrOutput1Sense anableyeeOutput1Sense anableyea<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —               |         |          |                                         |

| cfg_hclkInput1Configuration interface, AHB clockcfg_hresetnInput1Configuration interface, AHB reset, active-<br>lowcfg_haddrInputBITSConfiguration interface, AHB addresscfg_hmastlockInput3Configuration interface, AHB boxed<br>transfercfg_hmastlockInput4Configuration interface, AHB protectioncfg_hsizeInput4Configuration interface, AHB protectioncfg_hsizeInput3Configuration interface, AHB sizecfg_hvataInputBITSConfiguration interface, AHB write datacfg_hwriteInput1Configuration interface, AHB write datacfg_hreadyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readydata_outOutputecc_pins<br>+data_pinsData outputdata_out_enable_nOutput1Flash data outputoutput_enable_nOutput1Flash data output enableoutput_enable_nOutput1Sense anableyadrOutput1Sense anableyeeOutput1 </td <td>—</td> <td>•</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —               | •       |          |                                         |

| cfg_hresetnInput1Configuration interface, AHB reset, active-<br>lowcfg_hadrInputBITSConfiguration interface, AHB addresscfg_hburstInput3Configuration interface, AHB burst typecfg_hmastlockInput1Configuration interface, AHB burst typecfg_hrastInput3Configuration interface, AHB brotsetcfg_hrastInput4Configuration interface, AHB protectioncfg_htransInput3Configuration interface, AHB sizecfg_htransInput2Configuration interface, AHB write datacfg_hwataInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readydata_inInput1Configuration interface, AHB readydata_out_enableOutput1Data output enableoutput_enable_nOutput1Data output enablevadrOutput1Sense anableyadrOutput1X address enableyadrOutput1Y address enableyadrOutput1Y address enableyadrOutput1Y address enableyadrOutput1 <td< td=""><td>_</td><td>•</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _               | •       |          |                                         |

| Image: Construct of the second seco | —               | -       |          | -                                       |

| cfg_hburst<br>cfg_hmastlockInput3Configuration interface, AHB burst typecfg_hmastlockInput1Configuration interface, AHB locked<br>transfercfg_hprotInput4Configuration interface, AHB protectioncfg_hsizeInput3Configuration interface, AHB protectioncfg_htransInput2Configuration interface, AHB write datacfg_hwitaInput1Configuration interface, AHB write datacfg_hreadyInput1Configuration interface, AHB write datacfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB read datacfg_hreadyOutput1Configuration interface, AHB read datacfg_hreadyOutput1Configuration interface, AHB read datacfg_hreadOutput8TTSConfiguration interface, AHB read datacfg_hreadOutput1Configuration interface, AHB read datacfg_hreadOutput1Data outputdata_outOutputecc_pins<br>+data_pinsData outputdata_outOutput1Tata outputdata_out_enable_nOutput1Data output enable, active-lowxadrOutput1X address enableyedOutput1Y addressyadrOutput1Y address enableseOutput1Fase acycleyed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | cig_nieseth     | Input   | 1        |                                         |

| cfg_hburst<br>cfg_hmastlockInput3Configuration interface, AHB burst typecfg_hmastlockInput1Configuration interface, AHB locked<br>transfercfg_hprotInput4Configuration interface, AHB protectioncfg_hsizeInput3Configuration interface, AHB protectioncfg_htransInput2Configuration interface, AHB write datacfg_hwiteInput1Configuration interface, AHB write datacfg_hreadyInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB read datacfg_hreadyOutputBITSConfiguration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB readdata_outOutputecc_pins<br>+data_pinsData outputdata_out_enableOutput1Data outputdata_out_enable_nOutput1Tesh data output enable, active-lowxadrOutput1Yadress enableyeeOutput1Yaddress enableseOutput1Yaddress enableseOutput1Frase cycleyeeOutput1Hass erase cycleye                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | cfg_haddr       | Input   | BITS     | Configuration interface, AHB address    |

| cfg_hmastlockInput1Configuration interface, AHB locked<br>transfercfg_hprotInput4Configuration interface, AHB protectioncfg_hsizeInput3Configuration interface, AHB sizecfg_htransInput2Configuration interface, AHB transfer typecfg_hwdataInputBITSConfiguration interface, AHB write datacfg_hwataInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutputBITSConfiguration interface, AHB readycfg_hreadyOutputBITSConfiguration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readydata_inInputecc_pins<br>+data_pinsData outputdata_out_enableOutput1Data outputdata_out_enable_nOutput1Flash data output enableoutput_enable_nOutput1Y address enableyadrOutput1Y address enableseeOutput1Frase cycleyesOutput1Frase cycleyesOutput1Program cycleyesOutput1Program cycleyesOutput1Program cycleyesOutput1Program cycleyesOutput<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | cfg_hburst      | -       | 3        |                                         |

| cfg_hprotInput4Configuration interface, AHB protectioncfg_hprotInput3Configuration interface, AHB protectioncfg_hsizeInput3Configuration interface, AHB transfer typecfg_htransInputBITSConfiguration interface, AHB write datacfg_hwriteInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readydata_outOutput1Configuration interface, AHB readydata_outOutput1Data outputdata_out_enable_nOutput1Data outputoutput_enable_nOutput1Flash data output enable, active-lowxadrOutput1Yaddress enableyeeOutput1Yaddress enableyeeOutput1Yaddress enableyeeOu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cfg_hmastlock   | -       | 1        |                                         |

| cfg_hsizeInput3Configuration interface, AHB sizecfg_htransInput2Configuration interface, AHB transfer typecfg_hwdataInputBITSConfiguration interface, AHB write datacfg_hwriteInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadaOutputBITSConfiguration interface, AHB readycfg_hrespOutput1Configuration interface, AHB readydata_inInputecc_pins<br>+data_pinsData inputdata_out_enableOutput1Data outputoutput_enable_nOutput1Flash data output enableoutput_enable_nOutput1Flash data output enable, active-lowxadrOutputyadr_pinsColumn addressyadrOutput1Y address enableyeOutput1Sense amplifier enableifrenOutput1Frase cyclemassOutput1Program cycleyeOutput1Program cycleyeOutput1Recall triming codeseOutput1Recall triming codeseOutput1Recall triming codeseOutput1Recall trimi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _               | •       |          | -                                       |

| cfg_hsizeInput3Configuration interface, AHB sizecfg_htransInput2Configuration interface, AHB transfer typecfg_hwdataInputBITSConfiguration interface, AHB write datacfg_hreadyInput1Configuration interface, AHB readycfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readydata_inInputecc_pins<br>+data_pinsData outputdata_out_enableOutput1Data outputoutput_enable_nOutput1Flash data output enableoutput_enable_nOutput1Flash data output enable, active-lowxadrOutputyadr_pinsColumn addressyeOutput1Y address enableyeOutput1Sense anallifier enableifrenOutput1Frase cyclemas1Output1Has erase cyclemas1Output1Program cyclenvstrOutput1Recall trimming codeslmOutput1Selep mode enabletifrenOutpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | cfg hprot       | Input   | 4        | Configuration interface, AHB protection |

| cfg_htransInput2Configuration interface, AHB transfer typecfg_hwdataInputBITSConfiguration interface, AHB write datacfg_hwriteInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Data inputdata_out_enableOutput1Data outputdata_out_enableOutput1Flash data output enableoutput_enable_nOutput1Flash data output enableoutput_enable_nOutput1X addressyadrOutput1X address enableyadrOutput1Sense amplifier enableyadrOutput<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cfg hsize       |         |          |                                         |

| cfg_hwdataInputBITSConfiguration interface, AHB write datacfg_hwriteInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hselInput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutputBITSConfiguration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hrespOutput1Configuration interface, AHB readydata_inInputecc_pins<br>+data_pinsData inputdata_outOutput1Data output enableoutput_enableOutput1Flash data output enableoutput_enable_nOutput1Flash data output enable, active-lowxadrOutput1Yadress enableyadrOutput1Yaddress enableyeOutput1Yaddress enableyeOutput1Sense amplifier enableifrenOutput1Frase cyclemas1Output1Program cyclenvstrOutput1Recall trimming codeslmOutput1Recall trimming codeslmOutput1Recall trimming codeslmOutput1Selep mode enable </td <td>cfg htrans</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | cfg htrans      |         |          |                                         |

| cfg_hwriteInput1Configuration interface, AHB writecfg_hreadyInput1Configuration interface, AHB readycfg_hselInput1Configuration interface, AHB selectcfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutput1Configuration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB responsedata_inInputecc_pins<br>+data_pinsData inputdata_outOutput1Data outputdata_out_enableOutput1Data output enableoutput_enable_nOutput1Flash data output enable, active-lowxadrOutput1X addressyadrOutput1X addressyadrOutput1Y address enableyeOutput1Sense amplifier enableifrenOutput1Information block enableeraseOutput1Mass erase cyclemas1Output1Program cyclenvstrOutput1Recall trimming codeslmOutput1Recall trimming codeslmOutput1Recall trimming code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>cfg hwdata  |         |          |                                         |

| cfg_hreadyInput1Configuration interface, AHB readycfg_hselInput1Configuration interface, AHB selectcfg_hreadyOutput1Configuration interface, AHB readycfg_hreadyOutputBITSConfiguration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB read datadata_inInputecc_pins<br>+data_pinsData inputdata_outOutputecc_pins<br>+data_pinsData output enabledata_out_enableOutput1Flash data output enable, active-lowxadrOutput1Flash data output enable, active-lowxadrOutput1KadressyadrOutput1Y addressyadrOutput1Y addressyeOutput1Sense amplifier enableifrenOutput1Frase cyclemas1Output1Program cycleprogOutput1Non-volatile store cyclerecallOutput1Selep mode enableslmOutput1Selep mode enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>cfg hwrite  |         | 1        | -                                       |

| cfg_hselInput1Configuration interface, AHB selectcfg_hreadyOutput1Configuration interface, AHB readycfg_hrdataOutputBTTSConfiguration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB responsedata_inInputecc_pins<br>+data_pinsData inputdata_outOutputecc_pins<br>+data_pinsData outputdata_out_enableOutput1Data output enableoutput_enable_nOutput1Flash data output enable, active-lowxadrOutputxadr_pinsRow addressyadrOutput1X address enableyeOutput1Y address enableyeOutput1Sense amplifier enableifrenOutput1Frase cyclemas1Output1Program cycleprogOutput1Non-volatile store cyclenvstrOutput1Recall trimming codeslmOutput1Sleep mode enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br>cfg hready  | -       |          | -                                       |

| cfg_hreadyOutput1Configuration interface, AHB readycfg_hrdataOutputBITSConfiguration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB responsedata_inInputecc_pins<br>+data_pinsData inputdata_outOutputecc_pins<br>+data_pinsData output enabledata_out_enableOutput1Data output enableoutput_enable_nOutput1Flash data output enable, active-lowxadrOutputxadr_pinsColumn addressyadrOutput1X address enableyeOutput1Sense amplifier enableifrenOutput1Information block enableeraseOutput1Flask case cyclemas1Output1Mass erase cycleprogOutput1Non-volatile store cyclerecallOutput1Sleep mode enableitmrOutput1Sleep mode enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —               | -       |          | -                                       |

| cfg_hrdataOutputBITSConfiguration interface, AHB read datacfg_hrespOutput1Configuration interface, AHB responsedata_inInputecc_pins<br>+data_pinsData inputdata_outOutputecc_pins<br>+data_pinsData outputdata_out_enableOutput1Data output enableoutput_enable_nOutput1Flash data output enable, active-lowxadrOutputxadr_pinsRow addressyadrOutput1X address enableyeOutput1Y address enableseOutput1Sense amplifier enableifrenOutput1Information block enableeraseOutput1Mass erase cyclemas1Output1Program cycleprogOutput1Non-volatile store cyclerecallOutput1Sleep mode enabletrecallOutput1Sleep mode enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —               | -       |          | -                                       |