eSi-Connect

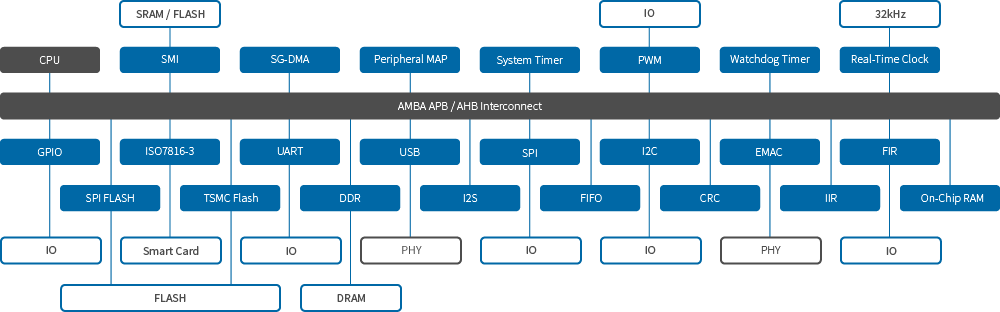

The eSi-Connect IP suite is a comprehensive range of processor peripherals each with standard AMBA AXI, AHB or APB interfaces to simplify SoC integration and connectivity.

The portfolio includes memory controllers (SMI, DDR, SPI Flash) as well as widely used off-chip interfaces such as USB, I2C, SPI and UART and control functions including Timer, Real-time Clock, Watchdog and GPIO. The blocks are configurable and provided with low-level software drivers suitable for real-time SoC deployment.

Download Documents